從Bring-up到Shift-left Siemens EDA以一致性工具鏈串起完善先進驗證流程

AI 時代的系統級晶片規模持續放大,軟硬體整合也更複雜,驗證團隊不僅要持續追求效率,更要在設計早期就能以接近真實系統的方式觀察行為,建立穩定、可複製的流程,來降低風險並推進專案時程。

為此,Siemens EDA於1月中旬舉辦「先進驗證技術日」,從硬體加速、FPGA原型到前期建模分析等路徑,說明如何以一致性工具鏈串起完整的端對端驗證流程,並透過客戶導入案例經驗分享與合作夥伴生態系資源介紹,讓與會者了解其中效益與優勢。

打擊關鍵痛點:Veloce proFPGA CS加速bring-up、設計分割與除錯

Siemens EDA資深產品經理Romain Petit首先概述新一代FPGA原型驗證技術的進展。他形容,要將複雜ASIC設計成功在原型平台上運作,「是一件真的很讓人頭痛、也最容易拖慢專案節奏的事;」而加速系統啟動(bring-up)的關鍵,在於平台必須可擴展且能彈性部署。

以 AMD Versal Premium VP1902 自適應SoC為核心的模組化設計Veloce proFPGA CS平台,涵蓋適合日常操作的單FPGA桌上型電腦,到伺服器/資料中心等級的多FPGA、數十億邏輯閘系統,並支援遠端管理與多專案共享,能依設計規模配置資源。

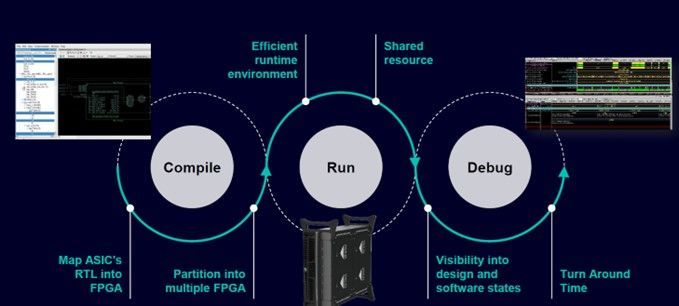

另一個重要的bring-up加速手段,是透過軟體將大量手動工程轉為可重現、可自動化的流程。Petit指出,由於ASIC與FPGA架構不可能一對一映射,加上時序收斂需要反覆迭代,介面協定整合與除錯高度複雜,若仰賴人工操作容易導致錯誤與結果不一致;VPS (Veloce Prototyping implementation Software)以「編譯-執行-除錯」(Compile–Run–Debug)三階段工作流程,將映射RTL至FPGA、多FPGA設計分割,以及高效率Runtime環境與共享資源、設計與軟體狀態的可視性等功能串聯起來,形成一致、可重複並持續最佳化的流水線,進而縮短周轉時間。

VPS的另一個核心功能是將多FPGA的設計分割與連線、時脈樹建置(包含閘控時脈轉換與時脈分配),以及記憶體處理(自動記憶體推斷、外部記憶體整合與軟體模型)等任務納入自動化,讓系統更快進入可運作狀態,再循序把效能推向最佳化。Petit強調,VPS透過支援批次(batch)與圖形化介面(GUI),協助使用者監控編譯流程與品質,並以設計註記、時脈樹與網表瀏覽、時序分析及分割檢視等機制提升除錯效率。

多FPGA原型驗證漸成常態,設計分割是專案能否落地、除錯能否有效推進的關鍵。Siemens EDA應用工程顧問David Lu指出,單一FPGA往往裝不下整體系統,若設計維持單體(monolithic)結構,實作與除錯難度會大增、資源管理也不易。透過合理分割可降低複雜度、改善時序與繞線可達性,並提升擴充與維護彈性。他補充,VPS支援在「全手動到全自動」間彈性取捨的分割策略:可人工主導切分與連線,或以自動化工具切分並建議互連以追求效能,也可先手動設定粗粒度約束再交由工具最佳化,兼顧bring-up速度與效能。

在除錯方面,David Lu表示VPS以串流化(streaming)架構為核心,支援多種觸發方式並可輸出波形供分析,在維持原型速度下提升可觀測性,縮短問題定位與除錯週期;搭配完整可視性與分組波形分析,使原型平台的除錯生產力更接近硬體模擬。同時透過結構化分割與自動分割的可預期品質與資源最佳化,再輔以手動調校提升效能與時序裕度,可在多FPGA架構下兼顧可靠度與長期擴展性。

來自 IC 設計業者凌陽(Sunplus)的代表也分享大型設計導入 proFPGA CS的實務經驗,聚焦原型驗證在除錯、波形觀測與環境建置上的常見痛點,對自動分割帶來的效率提升與工程便利性給予正向回饋。

從一致性到左移:System VIP、Innexis與車用開發實例

在原型bring-up與除錯之外,另一個挑戰是讓不同階段的驗證結果對齊,避免流程碎片化。Siemens EDA的系統級驗證IP (Avery VIP)研發經理Ken Huang指出,VIP的價值不只在經驗證的通訊協定IP,而是以「一致性核心」(unified kernel)維持跨階段對應關係(correlation),讓測試意圖與觀測結果能延伸到不同平台,提升一致性與效率。

另一方面,軟體架構師Marco Liu則強調「左移」(shift-left)的重要性。Siemens EDA的Innexis矽前(pre-silicon)虛擬平台,透過整合DevPro開發/除錯環境與ANA (Architecture Native Acceleration)原生加速,將高效能建模與分析移到RTL之前,使作業系統/應用程式與系統行為能更早運作、更快發現瓶頸,將驗證由後段補救轉為前段預防。

以車用SoC開發情境為實例,Siemens EDA資深客戶技術經理Charles Kuo指出,軟體定義車輛(SDV)促使車廠必須提升運算效能、縮短設計週期並支援長期OTA,然車輛硬體不但開發時程長、昂貴且不易變更;運用數位雙生平台(PAVE360),車廠可在硬體就緒前12~18個月就探索架構、開發軟體並進行系統級驗證,加速迭代收斂。

呼應此趨勢,Arm的Zena運算子系統(CSS)可透過與PAVE360的虛擬ECU、系統模型與情境模擬整合,協助將車用SoC開發到上車的週期壓縮至24~28個月。

從原型 bring-up、設計分割與除錯,到系統一致性驗證與前期建模分析,Siemens EDA以 Veloce搭配Innexis的硬體輔助方案實現驗證左移,串起矽前到系統層級的端對端流程,加速SoC、軟體與系統開發驗證。若想進一步了解Veloce與Innexis如何支援硬體加速驗證與系統級驗證策略,歡迎造訪官方網站。