先進封裝再進化! 解析NVIDIA GR150導入「CoWoP」的真正意義

AI與高效運算(HPC)進入爆發增長時代,晶片製程、摩爾定律推進趨緩,然而先進封裝技術已成為提升整體算力的關鍵戰場。

近期,市場流傳一份NVIDIA與供應鏈研發導入「CoWoP」的技術藍圖,這當中有甚麼值得觀察之處?以下為進一步的分析解讀。

從CoWoS到CoWoP 減去封裝基板受矚

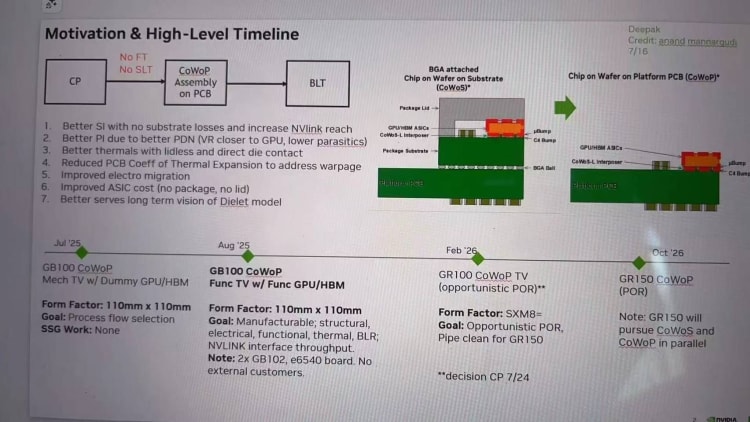

近期業界流傳一份名為「CoWoP」的全新封裝架構,亦即「Chip-on-Wafer-on-Platform PCB」的技術藍圖,據悉,為現有CoWoS的技術演進。

供應鏈業者透露,「CoWoP=CoWoS-基板」,據該資料顯示,CoWoP預計2026年10月在NVIDIA的GR150(Rubin)平台上實現,將是CoWoS與CoWoP「並行」的先進封裝策略。

台積電、NVIDIA將與日月光集團旗下的矽品、PCB、設備等供應鏈,預計2025年9月後,再研議討論450mmx450mm的可行性設計。

供應鏈業者表示,目前台積CoWoS(Chip-on-Wafer-on-Substrate),已成為特用晶片(ASIC)、NVIDIA H100、H200等更先進AI GPU的標配,其結構涵蓋晶片(GPU + HBM)、矽中介層(interposer)、封裝基板(Package Substrate),最終再以BGA方式焊接到伺服器主機板。

而據悉,CoWoP技術,簡單來說,就是「CoWoS減去封裝基板」。也就是將晶片與中介層組合後,直接安裝在強化設計的主機板(Platform PCB)上,跳過傳統的封裝基板與BGA步驟,主機板需直接承擔高精度訊號與電源佈線的功能。

這項「刪減封裝基板」一事,看似容易,但在技術層面上則難度相當高。

NVIDIA企圖再建構護城河 CoWoP帶來七大改變

供應鏈業者表示,NVIDIA正計劃透過CoWoP,將原本集中於晶片製程的性能瓶頸,轉移至封裝與系統級互連,以此建立新的技術護城河。

整體而言,目標就是透過高度系統整合與平台定義權,主導未來AI晶片的標準。

據供應鏈流傳的技術藍圖分析,CoWoP未來可帶來「七大改變」,包括:

一、訊號完整性(SI)提升:省去一層封裝基板,訊號路徑更短、更直接,NVLink和HBM通訊損耗顯著降低,傳輸距離可延長。

二、電源完整性(PI)強化:電壓調節器可更靠近GPU,減少寄生參數。

三、散熱效能提升:取消晶片上蓋(lid),晶片直接接觸,帶來更佳散熱效果。

四、降低PCB熱膨脹係數,解決翹曲問題。

五、改善電遷移(Electromigration)。

六、降低ASIC成本(無封裝、無蓋子)。

七、支援更彈性的晶片模組整合方式,邁向無封裝架構長期願景。

CoWoP有四大挑戰 載板技術成熟度高

不過,業界人士指出,CoWoP面對的挑戰仍不少,包括:

其一,主機板技術門檻大幅提高,Platform PCB必須具備封裝等級的佈線密度、平整度與材料控制。

其二,返修與良率壓力劇增,GPU裸晶直接焊接主機板,失敗即報廢,製程容錯空間低。

其三,系統協同設計更複雜,增加開發成本。

其四,技術轉移成本高。

供應鏈認為,此一技術若順利推進,主機板轉變為晶片的「最後一層封裝」,不僅能降低整體成本,更將主導AI硬體平台的定義權。

不過也仍有PCB業者認為,目前載板技術相對成熟,價格合理,CoWoP欲取代傳統封裝,仍需時間。

儘管如此,目前市場盛傳的技術藍圖資料仍顯示,CoWoP已在2025年7月,被列入稱為GB100的內部測試平台中,預計2026年10月在GR150平台上,實現CoWoS與CoWoP並行封裝策略。

業界推估,台積、NVIDIA將與封測端的矽品、PCB、設備等供應鏈,在2025年9月供應鏈論壇後,可望再研議討論450mmx450mm尺寸可行性設計。

而據DIGITIMES Research初步分析,GB100、GR150等,推估是NVIDIA內部工程測試品,例如用上一世代的Grace CPU,搭配這一代的Rubin GPU平台,或是Blackwell GPU平台,進行先進封裝技術的各種研發討論,並不一定會商品化對外銷售,但在Vera CPU新平台整裝上陣前,持續進行技術開發。

儘管如此,NVIDIA攜手台積電等供應鏈,多方大膽嘗試先進封裝的進化可能性,確實是現在進行式。預計2026年的半導體先進封裝技術發展,更為精彩。

責任編輯:何致中