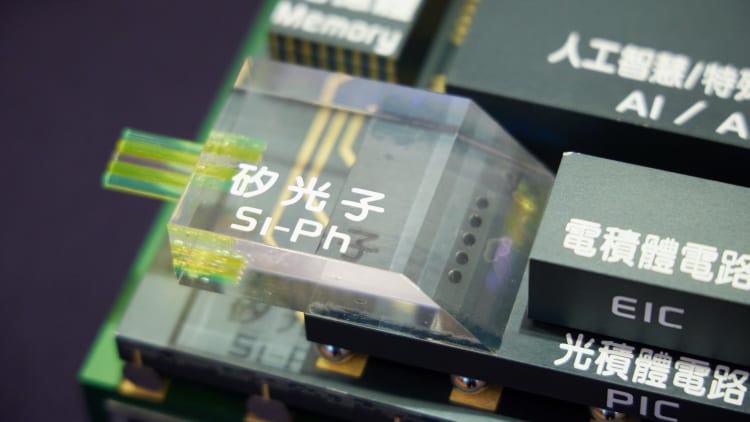

矽光子量產壓力落晶圓測試鏈 「上電下光」結構成關鍵

隨著AI算力需求將高速傳輸效率推向極限,2026年被視為矽光子(SiPh)與光學共同封裝(CPO),走向規模化部署的關鍵元年,更成為業界迫切布局的全新戰場。

值得注意的是,這場矽光子量產大戰的成敗關鍵,如今已落到半導體測試供應鏈的肩頭上。

封測業界人士指出,矽光子晶片測試共有三道工序,而當前最棘手的量產障礙,就卡在「上電下光」的晶圓級光電整合測試,因其位處測試介入製程的第二道程序,業界也將之稱為「Insertion 2」。

其中,由於台積電採SoIC技術,將電子晶片(EIC)與光子晶片(PIC)進行垂直堆疊,因此,其所產出的緊湊型通用光子引擎(COUPE),必須通過上電下光的雙邊晶圓測試,才能進一步篩選出不良品與良品。

據了解,最核心的技術瓶頸在於,由於光、電訊號的測試條件存在明顯差異,市場上尚不具備可用於量產的自動化測試解決方案。

因此,Insertion 2也被半導體業界視為矽光子測試的「一大黑洞」,不僅測不快、更量不準。

換言之,如何開發出低成本且有效率的自動化測試解決方案,正高度考驗自動化測試設備(ATE)與測試介面供應商的技術開發能力,若未能突破瓶頸實現經濟規模效益,短期內也恐將大幅降低市場的採用意願。

據了解,在客戶端量產時程壓力下,測試設備大廠愛德萬測試(Advantest)、泰瑞達(Teradyne),以及測試介面大廠FormFactor、旺矽、漢民測試等關鍵廠商,正加速投入自動化測試解決方案開發,跨越晶圓級光電整合測試的障礙,力求搶先插旗這座灘頭堡。

此外,供應鏈提到,矽光子晶片測試的另外兩道工序,分別為對應光子IC測試、CPO封裝後成品測試的「Insertion 1」、「Insertion 3」,市場上目前已有相對成熟的自動化解決方案。

針對Insertion 1產品布局,愛德萬指出,與FormFactor合作開發的整合解決方案「Triton」,現已在客戶端進行設備調適,預期可在年底前正式落地,進一步支援PIC測試的實戰。

至於關鍵量產瓶頸的Insertion 2,愛德萬與供應鏈夥伴提出的解決方案,則預計在上半年完成可行性驗證(proof of concept),並有望在下半年進入與客戶共同開發階段。

業界分析,矽光子晶片在高速傳輸環境下,對穩定性與準確度的要求顯著提高,使整體測試技術門檻同步攀升,尤其經過CPO封裝完成的矽光子晶片,一旦測出失效、代價極為高昂,測試左移(Shift-Left Testing)的重要性大增,分階段的驗證被視為守住利潤的最後防線。

不過,供應鏈人士透露,若上電下光的測試瓶頸,遲遲無法在設備上獲得突破,測試廠不排除在量產初期選擇性跳過Insertion 2,將勝算押注在解決方案明確的Insertion 3,以犧牲部分良率與成本的折衷方案,來換取最終產品如期量產出貨。

責任編輯:何致中